お客さまの声

業務内容

ご要求仕様通りに要求仕様書より、設計仕様書、検証仕様書を作成し、VerilogHDLにてコーディングを行い、RTLレベルのシミュレーション後、ソース、ドキュメントを納品させて頂きます。

※年末年始も稼働しております。

基本料金

出品者

すみませんが、休業中です。

-

0 満足0 残念

- 本人確認

- 個人

30年ほど東京でデバイス開発をしておりました。各メーカー様開発、及び汎用のEWSを経て、VerilogHDL、VHDLによる設計、Synopsysによる回路合成を行っておりました。開発に携わったデバイスは100以上になります。昔はPCの拡張ボード、ICE設計の補助、最近は、LAMP構成によるEラーニングシステム、不動産物件の管理システムを構築しました。ZENサーバーを使用したこともあります。

自宅での作業となりますので、残念ながら機材が限られます。

NAND換算で数千から1桁万ゲート程度の、デバイス内に組み込まれる、1ブロックのRTL設計を担当させて頂くことを望んでおります。

【主に頂きたいドキュメントや情報】

・ブロックの基本動作仕様書

完全に仕上げるには時間が掛かりますので、ある程度の断片情報を頂きまして動作説明ドキュメントにまとめさせて頂くことも可能です

・クロックの系統が複数

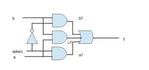

複数系統ある場合、そのデータを他クロックに乗り入れる際、メタステーブルを避けるため、F/F2段で一度同期をとります。また、完全に非同期な入力に対しても同様な処置をします

・クロックのドライブ

概ねチップ全体で、その系統のクロックにCTSにてスキューの整合性を図ります。RTLでは特に考慮しません。直接使いますので、例外ケースはお教えください。

また、あまりないケースですが、そのブロック内にCTSを持たせる場合は、非同期なブロックとして扱うのが安全です

・インプット、アウトプットのAC/DCタイミング

どのようにして作られた入力か、周波数レート、パルス幅、完全非同期、特定のクロックに同期、また、どのように出力すればよいか、クロックで同期した後に組み合わせ回路が多くタイミング的に不安な場合、最終段で一度F/Fで切ったりしますが、その際にはクロックが一つずれるので、デバイス全体としての考慮が必要です

【納品物 VelilogHDL】

・ブロック本体のRTL

・ブロックを検証するためのテストベンチ(RTL)

・ブロック内のRTL構成及び動作説明ドキュメント

・テストベンチにおける動作チェック項目ドキュメント。単純な個所は目視チェックを行って頂く事があります

第四級アマチュア無線技士の資格を保有しております。

多少ですが、他方面の原稿執筆や校正を行っていたこともあります。

※年末年始も稼働しております。

よろしくお願い申し上げます。

注文時のお願い

・お仕事の打診を頂きました場合、システム、ご予算を詰めさせて頂けますでしょうか。表記の開発期間と予算は目安とお考えください。

メールにて、頻繁にご連絡をとらせて頂けましたら幸いです。

よろしくお願い申し上げます。